River Publishers Series in Communications and Networking

Key Enabling Technologies for Future Wireless, Wired, Optical and Satcom Applications

Björn Debaillie Philippe Ferrari Didier Belot François Brunier Christophe Gaquiere Pierre Busson Urtė Steikūnienė

# **Key Enabling Technologies for Future Wireless, Wired, Optical and Satcom Applications**

# RIVER PUBLISHERS SERIES IN COMMUNICATIONS AND NETWORKING

Series Editors

#### ABBAS JAMALIPOUR

The University of Sydney Australia

#### MARINA RUGGIERI

University of Rome Tor Vergata Italy

The "River Publishers Series in Communications and Networking" is a series of comprehensive academic and professional books which focus on communication and network systems. Topics range from the theory and use of systems involving all terminals, computers, and information processors to wired and wireless networks and network layouts, protocols, architectures, and implementations. Also covered are developments stemming from new market demands in systems, products, and technologies such as personal communications services, multimedia systems, enterprise networks, and optical communications.

The series includes research monographs, edited volumes, handbooks and textbooks, providing professionals, researchers, educators, and advanced students in the field with an invaluable insight into the latest research and developments.

Topics included in this series include:-

- · Communication theory

- Multimedia systems

- · Network architecture

- Optical communications

- Personal communication services

- · Telecoms networks

- Wi-Fi network protocols

For a list of other books in this series, visit www.riverpublishers.com

# **Key Enabling Technologies for Future Wireless, Wired, Optical and Satcom Applications**

#### **Editors**

# Björn Debaillie

imec, Belgium

## Philippe Ferrari

Université Grenoble Alpes, France

### **Didier Belot**

STMicroelectronics, France

# François Brunier

Soitec, France

## **Christophe Gaquiere**

MC2 Technologies, France

## Pierre Busson

STMicroelectronics, France

#### Urtė Steikūnienė

Teraglobus, Lithuania

#### **Published 2024 by River Publishers**

River Publishers Alsbjergvej 10, 9260 Gistrup, Denmark www.riverpublishers.com

#### Distributed exclusively by Routledge

605 Third Avenue, New York, NY 10017, USA 4 Park Square, Milton Park, Abingdon, Oxon OX14 4RN

Key Enabling Technologies for Future Wireless, Wired, Optical and Satcom Applications / Björn Debaillie, Philippe Ferrari, Didier Belot, François Brunier, Christophe Gaquiere, Pierre Busson, and Urté Steikūnienė

©2024 River Publishers. All rights reserved. No part of this publication may be reproduced, stored in a retrieval systems, or transmitted in any form or by any means, mechanical, photocopying, recording or otherwise, without prior written permission of the publishers.

Routledge is an imprint of the Taylor & Francis Group, an informa business

ISBN 978-87-7004-665-7 (hardback) ISBN 978-87-7004-667-1 (online) ISBN 978-8-770-04666-4 (ebook master)

While every effort is made to provide dependable information, the publisher, authors, and editors cannot be held responsible for any errors or omissions.

#### **Open Access**

This book is distributed under the terms of the Creative Commons Attribution-Non-Commercial 4.0 International License, CC-BY-NC 4.0) (http://creativecommons.org/licenses/by/4.0/), which permits use, duplication, adaptation, distribution and reproduction in any medium or format, as long as you give appropriate credit to the original author(s) and the source, a link is provided to the Creative Commons license and any changes made are indicated. The images or other third party material in this book are included in the work's Creative Commons license, unless indicated otherwise in the credit line; if such material is not included in the work's Creative Commons license and the respective action is not permitted by statutory regulation, users will need to obtain permission from the license holder to duplicate, adapt, or reproduce the material.

The use of general descriptive names, registered names, trademarks, service marks, etc. in this publication does not imply, even in the absence of a specific statement, that such names are exempt from the relevant protective laws and regulations and therefore free for general use.

The publisher, the authors and the editors are safe to assume that the advice and information in this book are believed to be true and accurate at the date of publication. Neither the publisher nor the authors or the editors give a warranty, express or implied, with respect to the material contained herein or for any errors or omissions that may have been made.

Printed on acid-free paper.

#### **Dedication**

"The combined results of several people working together is often more effective than an individual scientist working alone."

John Bardeen

"Imagination is more important than knowledge. For knowledge is limited to all we now know and understand, whereas imagination embraces the entire world."

Albert Einstein

"Thoroughly conscious ignorance is the prelude to every real advance in science."

James Clerk Maxwell

## Acknowledgement

The editors would like to thank all the contributors for their support in the planning and preparation of this book. The recommendations and opinions expressed in the book are those of the editors, authors, and contributors and do not necessarily represent those of any organizations, employers, or companies.

Björn Debaillie Philippe Ferrari Didier Belot François Brunier Christophe Gaquiere Pierre Busson Urt Steik nien

# **Contents**

| Pr | eface                                                                                                                                                                                                                                                                                                                        | xi    |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|

| Ed | litors' Biography                                                                                                                                                                                                                                                                                                            | xix   |

| Li | st of Contributors                                                                                                                                                                                                                                                                                                           | xxiii |

| Li | st of Figures                                                                                                                                                                                                                                                                                                                | xxix  |

| Li | st of Tables                                                                                                                                                                                                                                                                                                                 | xli   |

| 1. | <b>B55X:</b> A SHIFT in STMicroelectronics BiCMOS Technologies <i>P. Chevalier, Member, IEEE, A. Gauthier, N. Guitard, V. Milon, F. Monsieur, N. Derrier, C. Deglise-Favre, D. Céli, C. Durand, O. Foissey, F. Sonnerat, F. Gianesello, D. Gloria</i>                                                                        | 1     |

| 2. | RF Technology Roadmap for 5G and 6G RF Front-end Systems Yvan Morandini                                                                                                                                                                                                                                                      | 13    |

| 3. | Advanced Substrate Technologies for Sub-THz Era François Brunier                                                                                                                                                                                                                                                             | 21    |

| 4. | A CMOS Compatible III-V-on-300 mm Si Technology<br>for Future High-speed Communication Systems:<br>Challenges and Possibilities<br>A. Vais, A. Kumar, G. Boccardi, S. Yadav, Y. Mols, R. Alcotte,<br>B. Vermeersch, M. Ingels, U. Peralagu, C. Roda Neve, B. Ghyselen,<br>B. Parvais, P. Wambacq, B. Kunert, and N. Collaert | 27    |

| 5. | The Impact of Irradiation on DC Characteristics and Low-Frequency Noise of Advanced SiGe:C HBTs  B. Sagnes, A. Adebabay Belie, M. Bouhouche, J. El Beyrouthy, F. Pascal, J. Boch, P. Chevalier, and D. Gloria                                                                                                                | 41    |

| 6.  | <b>D-band Modulated Signal Generation using Photonics Techniques</b> Y. M. Wodaje, B. Baridi, O. Occello, F. Danneville, P. Szriftgiser, and G. Ducournau                                                                                                                                                                                                        | 53  |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 7.  | Decarbonizing the Electronics Industry to Achieve<br>Net Zero (2024)<br>Gunther Walden                                                                                                                                                                                                                                                                           | 59  |

| 8.  | Analog Multiplexing for Bandwidth and Sampling Rate<br>Multiplication of Digital–Analog Converters in Coherent<br>Optical Transmission Systems<br>Oliver Hauck, Fred Buchali, Michael Collisi, and<br>Michael Möller                                                                                                                                             | 67  |

| 9.  | Challenges for 2.5D and 3D Integration of InP HBT Technology Bertrand Ardouin, Tom K. Johansen, Antoine Chauvet, Romain Hersent, Virginie Nodjiadjim, Agnieszka Konczykowska, Nil Davy, Muriel Riet and Colin Mismer                                                                                                                                             | 81  |

| 10. | . Analysis of Quasi-Coaxial Via Implemented in<br>IC Substrate using Multiple-Scattering Method<br>Hiroaki Takahashi, Pelin Suealp, and Erich Schlaffer                                                                                                                                                                                                          | 91  |

| 11. | A. Fonte, S. Moscato, R. Moro, A. Pallotta, A. Mazzanti, A. Bilato, G. De Filippi, L. Piotto, F. Centurelli, P. Monsurrò, H. Sadeghi Chameh, P. Tommasino, A. Trifiletti, D. Lodi Rizzini, F. Tesolin, S. M. Dartizio, and S. Levantino                                                                                                                          | 101 |

| 12. | Communications G. Mangraviti, C. Dehos, V. Puyal, O. Richard, G. Yaakoubi khbiza, F. Foglia Manzillo, X. V. L. Nguyen, F. Filice, E. Noccetti, P. L. Hellier, F. Podevin, S. Bourdel, A. Ruffino, KS. Choi, B. Abdelaziz Abdelmagid, M. Eleraky, H. Wang, B. Ardouin, T. K. Johansen, L. Fanori, Q. Huang, E. Schlaffer, P. Wambacq, D. Morche, and B. Debaillie | 115 |

| 13. Ka-Band GaN-on-SiC Power Amplifier for High EIRP Satellite Phased Antenna Array Francesco Manni, Paolo Colantonio, Rocco Giofrè, Ernesto Limiti, Patrick Ettore Longhi, Steven Caicedo Mejillones, Stefano Moscato, and Alessandro Fonte | 133 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Appendix                                                                                                                                                                                                                                     |     |

| 14. InP on Si Technologies for Next-Generation Optical<br>Communication High-speed Analog Front-Ends<br>Romain Hersent                                                                                                                       | 145 |

| 15. 150 nm Gallium Nitride on Silicon Carbide Technology for<br>High-power 5G New Radio Applications<br>Kimon Vivien                                                                                                                         | 149 |

| 16. Post-process Substrate Porosification for RF Applications  Joff Derluyn                                                                                                                                                                  | 151 |

| 17. A Multi-standard RF Bandpass Sigma-Delta ADC Hassan Aboushady                                                                                                                                                                            | 153 |

| 18. D-band RF Architecture for Beyond 5G Wireless Networks:<br>Specifications, Challenges, and Key Enabling Technologies<br>Cedric Dehos                                                                                                     | 155 |

| 19. E-band and D-band VCOs: Distributed Tank Design<br>Methodology, Bufferless Approach<br>Leonardo Gomes                                                                                                                                    | 157 |

| 20. 2.5D, 3D Assembly Technologies for RF, mmW and Sub-THz<br>Heterogeneous Systems<br>Valorge Olivier                                                                                                                                       | 159 |

| 21. Heterointegration Approaches for InP-HBT Technologies for 5G Applications and Beyond Hady Yacoub                                                                                                                                         | 163 |

| 22. RF-Heterointegration at Wafer-level and Panel-level for mmWave Applications Siddhartha Sinha                  | 165 |

|-------------------------------------------------------------------------------------------------------------------|-----|

| 23. SiGe BiCMOS & III-V Technologies Heterogeneous Integration Challenges Frederic Gianesello                     | 167 |

| <b>24.</b> Advanced Packaging Solutions for mmWave Applications <i>Tanja Braun</i>                                | 169 |

| 25. Modular 3D mmW and THz Packaging Concepts and Technologies  Mikko Varonen                                     | 171 |

| 26. LDS and AMP Processes for RF Antenna in Package (AiP) Applications in the E- and D-Bands Abdel Hadi Hobballah | 173 |

| 27. Sub-THz Antenna and Package Integration for Miniaturized Surface-Mount Device Modules  Akanksha Bhutani       | 175 |

| Index                                                                                                             | 177 |

# **Preface**

# Key enabling technologies for future wireless, wired, optical and satcom applications

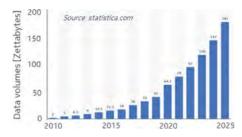

As our interconnected world continues to expand, the importance of global innovation in communication systems and technologies grows significantly. Our increasing reliance on digital communication demands systems offering higher data traffic, providing faster and more reliable connectivity, and sustainably support a diverse range of applications. The demand for improved communication technologies has never been more urgent, necessitating substantial advancements and strategic shifts in today's development and implementation approaches.

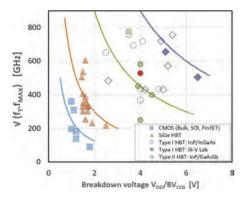

Realizing these goals requires a transition towards higher frequency bands, such as mm-wave and sub-THz, and the adoption of disruptive technologies. These advanced frequency bands facilitate greater data transfer rates and lower latency, essential for enabling next generation communication networks. Venturing into higher frequency bands above 100 GHz for 6G further necessitates the utilisation of disruptive semiconductor technologies, including heterogeneous integration of (Bi)CMOS, SOI, and III/V components such as GaN or InP, alongside advanced packaging techniques. These innovations will play a pivotal role in achieving the objectives of ubiquitous, compact, efficient, and high-performance systems.

However, as we push the boundaries of technological possibilities, it is imperative to consider the environmental impact of these innovations. Ensuring that future communication systems are not only technologically advanced but also sustainable and responsible is paramount. This entails careful consideration of the materials used/handled, manufacturing processes employed, operational efficiency, and their recyclability. Addressing these environmental factors is essential for developing technologies that meet our communication needs while safeguarding the planet for future generations.

This book illustrates the latest research roadmaps and achievements from the European ecosystem, comprising industry, research, and academia. It focuses on the development of future wireless, wired, optical, and satellite communication (satcom) applications utilizing the mm-wave and sub-THz bands. Encompassing the entire value chain, the book explores technologies, devices, characterization, architectures, circuits, 3D heterogeneous integration, and advanced packaging techniques.

Leveraging the synergetic interactions between European CHIPS JU projects SHIFT and Move2THz, the European 3D heterogeneous integration and packaging community, and the MTT-TC9 society, this book highlights transformative developments in communication technology. The SHIFT project pioneers innovative semiconductor and packaging technologies for telecommunication areas such as 5GNR (Beyond 5G) and 6G wireless, satellite and optical networks and Earth observation. The Move2THz project is instrumental in transforming the InP platform and establishing a fully integrated European value chain, providing commercially attractive, eco-friendly, mass-market technologies suitable for sub-THz frequency operation and beyond. The IEEE MTT-TC9 society's mission is to monitor developments in emerging and technologically significant solid-state device technologies for microwave and/or mm-wave applications and promote the dissemination and sharing of technical knowledge in those areas.

The book comprehensively covers the topics discussed at the International Workshop on "Key Enabling Technologies for Future Wireless, Wired, Optical, and Satcom Applications," held at the European Microwave Week in Paris, France, on September 22, 2024. Through articles and abstracts, it provides a combined view of experts and practitioners representing academia, research, and industry in the field of wireless and optical communication systems. The workshop spans a wide range of topics, including device and substrate characterization, circuit and antenna design, and integration and packaging technologies. All of which are crucial for advancing high-performance and sustainable communication applications.

This book is a valuable resource for researchers, designers, developers, academics, post-graduate students and practitioners seeking recent research results on 5G and 6G technology. It combines several novel developments and collaborative initiatives across the entire value chain, from substrate technology up to applications. As such, it provides a comprehensive understanding of the scientific path forward and underscores the critical role of sustainable and responsible innovation in this rapidly evolving landscape.

The book is structured into 12 articles and 15 abstract descriptions, which are distributed over 5 topic clusters. Each cluster provides a comprehensive overview of the advancements and innovations within a specific domain of

communication technology. Together, these clusters offer a comprehensive exploration of the latest research and developments shaping the landscape of communication technology, providing valuable insights for researchers, designers, and practitioners in the field.

The first cluster focuses on substrate technology innovations, highlighting their pivotal role in enabling emerging applications in communication systems.

- Pascal Chevalier, Alexis Gauthier, Nicolas Guitard, Victor Milon, Frederic Monsieur, Nicolas Derrier, Claire Deglise-Favre, Didier Céli, Cédric Durand, Ophélie Foissey, Florence Sonnerat, Frederic Gianesello, Daniel Gloria: "B55X: A SHIFT in STMicroelectronics BiCMOS Technologies" presents why BiCMOS055X is also a significant shift in STMicroelectronics BiCMOS offer, first in terms of innovation and performances, but also with respect to the device offer that has been tailored to address different applications, turning out in a flexible technology offer.

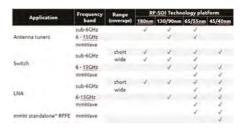

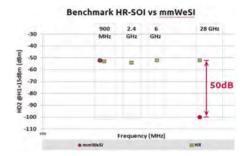

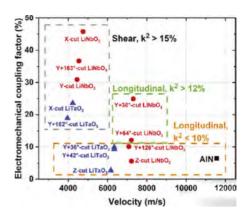

- *Yvan Morandin*: "RF advanced substrates for 5G advanced and 6G" presents the RF substrate technology roadmap, crucial for architecting the resilient, high-performance RF systems that will underpin the next gen 5G and 6G wireless infrastructure.

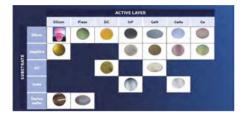

- *Francois Brunier*: "Advanced substrates technologies for Sub-THz era" describes how FD-SOI ecosystem innovation on III-V innovative substrates solutions can enable novel sub-THz applications.

- Abhitosh Vais, Annie Kumar, Guillaume Boccardi, Sachin Yadav, Yves Mols, Reynald Alcotte, Bjorn Vermeersch, Mark Ingels, Uthayasankaran Peralagu, César Roda Neve, Bruno Ghyselen, Bertrand Parvais, Piet Wambacq, Bernardette Kunert, Nadine Collaert: "A CMOS compatible III-V-on-300mm Si technology for future high speed communication systems" arguments for the upscaling of III-V technology on to 300mm Si platforms and presents how to achieve its integration into existing CMOS platform.

- \*Romain Hersent: "InP-on-Si Technologies For Next Generation Optical Communication High-Speed Analog Front-Ends" discuss the challenges related to the design of large-swing, high-efficiency and extreme-high-symbol-rate analog electronics integrated circuits for next generation >1.6T optical /6G communication systems.

- \*Kimon Vivien: "150nm Gallium Nitride on Silicon Carbide Technology for High Power 5G New Radio Applications" describes the 150nm Gallium Nitride on Silicon Carbide technology of UMS, with a focus on high power, sub-6 GHz applications.

The second cluster delves deeper into advancing high-frequency device technology modelling and enhancing the sustainability of electronics, addressing critical challenges in the field.

- \*Joff Derluyn: "Post-process substrate porosification for RF applications" proposes a process to the handle silicon substrate after and independently from the fabrication of the front side RF circuitry to achieve extremely low harmonic distortion and microwave losses, far out-performing RF-SOI.

- Bruno Sagnes, Ayenew Adebabay Belie, Menel Bouhouche, Johnny El Beyrouthy, Fabien Pascal, Jérôme Boch, Pascal Chevalier, Daniel Gloria: "The impact of irradiation on DC characteristics and Low Frequency Noise of advanced SiGe:C HBTs" presents their investigated X-ray and gamma total ionizing dose impacts on advanced SiGe:C HBTs supplied by STMicroelectronics.

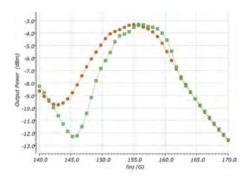

- Yewulsew Manale Wodaje, Bachar Baridi, Olivier Occello, François Danneville, Pascal Szriftgiser, Guillaume Ducournau: "D-band modulated signal generation using photonics techniques" addresses a photonics approach to generate modulated signals in the range 110-170 GHz.

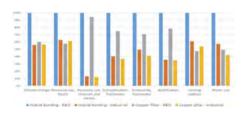

- *Gunther Walden*: "Decarbonizing the electronics industry to achieve Net Zero" describes essential questions and approaches to address the United Nations net-zero emissions target for 2050.

In the third cluster, innovative circuit design and architectures for high-speed communication are explored, showcasing cutting-edge developments in this rapidly evolving area.

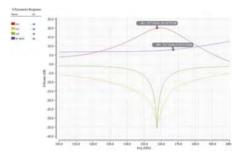

- \*Hassan Aboushady: "A multi-standard RF Bandpass Sigma-Delta ADC" presents a 65 nm CMOS LC resonator-based tunable bandpass RF Sigma-Delta modulator with a centre frequency from 1.5 to 3.0 GHz and a corresponding sampling frequency from 6.0 to 12.0 GHz.

- Oliver Hauck, Fred Buchali, Michael Collisi, Michael Möller: "Analog Multiplexing for Bandwidth and Sampling Rate Multiplication of DACs in Coherent Optical Transmission Systems" presents 2:1 and 4:1 analog time division multiplexing circuit concepts, a frequency domain ENoB-model approach and measurement results.

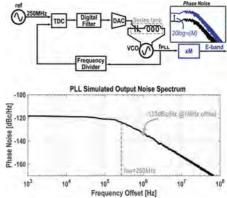

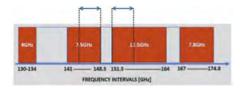

- \*Cédric Dehos: "D-Band RF architecture for Beyond 5G wireless networks" discusses the challenges of D-band transceiver design with integrated scalable and reconfigurable antennas.

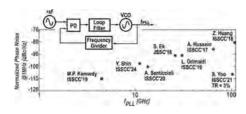

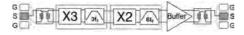

\*Leonardo Gomes: "E-band & D-band VCOs: distributed tank design methodology, bufferless approach" proposes a new methodology to design mm-wave VCOs based on distributed resonators using a global optimization routine.

The fourth cluster examines technology-level heterogeneous integration approaches, demonstrating how these strategies can enhance characteristics and performance across various applications.

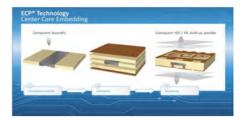

- \*Olivier Valorge: "2.5D, 3D assembly technologies for RF, mmW and sub-THz heterogeneous systems" described different 2.5D & 3D integration solutions from the simplest to the most advanced while focusing on mmW/subTHz heterogeneous integrated systems.

- \*Hady Yacoub: "Heterointegration approaches for InP-HBT technologies for 5G applications and beyond" presents an overview of heterointegration techniques, their RF performance, and their scalability roadmap towards higher frequencies.

- \*Siddhartha Sinha: "RF-Heterointegration at Wafer-level and Panel-level for mm-wave Applications" presents different mm-wave packaging technologies, including RF-optimized waferscale silicon interposer technologies and PCB embedded Air-Filled Waveguides.

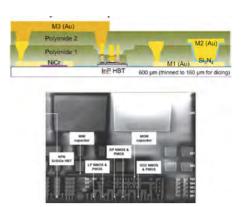

- Bertrand Ardouin, Tom Keinicke Johansen, Antoine Chauvet, Romain Hersent, Virginie Nodjiadjim, Agnieszka Konczykowska, Nil Davy, Muriel Riet, Colin Mismer: "Challenges for 2.5D and 3D integration of InP HBT technology" reviews the key specificities of InP DHBT technologies and highlights their 2.5 and 3D integration challenges.

- \*Frederic Gianesello: "SiGe BiCMOS & III-V technologies heterogeneous Integration challenges" reviews different heterogeneous integration with III-V technologies and their associated challenges by discussing SiGe BiCMOS heterogeneous integration with GaN on SiC and InP technologies.

Finally, the fifth cluster explores disruptive system design, integration, and packaging technologies, particularly focusing on their role in enabling future (sub-)THz and optical applications.

\*Tanja Braun: "Advanced Packaging Solutions for mmWave Applications" introduces advanced packaging solutions suitable for RF and mmWave applications and antenna-in-package solutions, shielding

- on package level, passive component integration or heterogeneous integration of III/V semiconductors with Si or SiGe in one package.

- \*Mikko Varonen: "Modular 3D mmW and THz packaging concepts and technologies" focusses on packaging techniques for efficient phased array scaling and VTT's 3D modular packaging concepts for heterogeneous integration of different MMIC technologies.

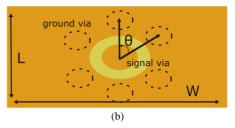

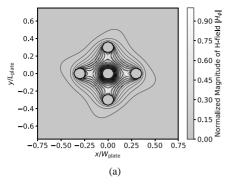

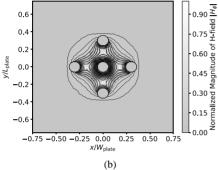

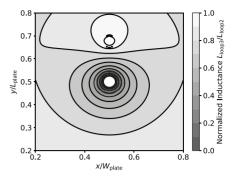

- Hiroaki Takahashi, Pelin Suealp, Erich Schlaffer: "Analysis of Quasi-Coaxial Via implemented in IC Substrate using Multiple Scattering Method" presents numerical simulation- and measurement-based characterization of interconnections implemented in organic IC-substrates for 6G communication.

- \*Abdel Hadi Hobballah: "LDS and AMP processes for RF antenna in package AiP applications in the E and D-band" discusses the LDS laser direct structuring technology for the manufacturing of advanced component packaging for Antenna-in-Package (AiP) solutions operating within the E and D bands.

- \*Akanksha Bhutani: "Sub-THz Antenna and Package Integration for Miniaturized Surface Mount Device Modules" describes antenna and package developments focussing on miniaturized surface-mount devices in the WR6 (110 170 GHz), WR3 (220 325 GHz) and WR2.2 (325 500 GHz) bands.

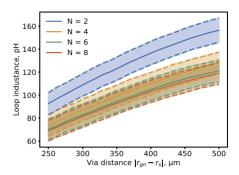

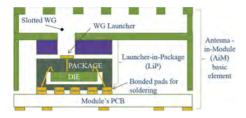

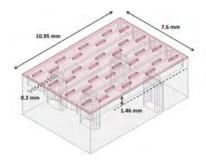

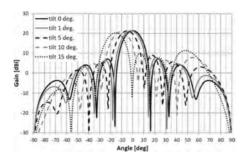

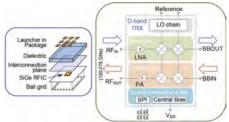

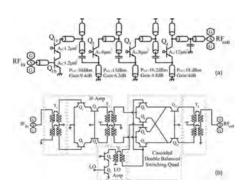

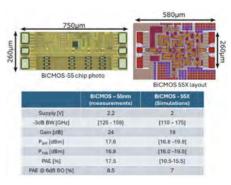

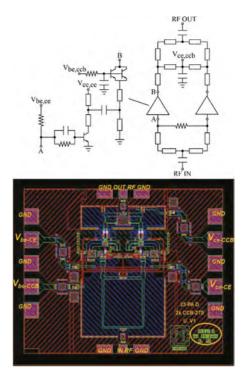

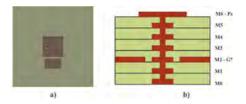

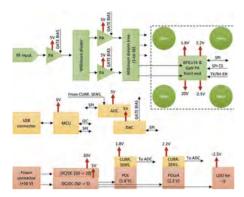

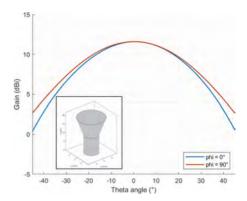

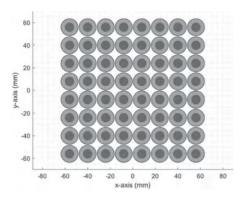

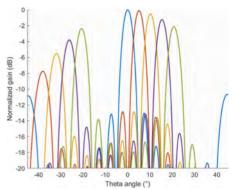

- Alessandro Fonte, Stefano Moscato, Riccardo Moro, Andrea Pallotta, Andrea Mazzanti, Andrea Bilato, Guglielmo De Filippi, Lorenzo Piotto, Francesco Centurelli, Pietro Monsurrò, Hassan Sadeghi Chameh, Pasquale Tommasino, Alessandro Trifiletti, Daniele Lodi Rizzini, Francesco Tesolin, Simone Mattia Dartizio, Salvatore Levantino: "D-band Phased Array Antenna Module for 5G Backhaul" presents advancements of the basic element of the D-band phased array antenna system through a mockup of the module and the package, the D-band antenna concept and the RFICs developed by using the cutting-edge STMicroelectronics 55nm and 55X SiGe BiCMOS technologies.

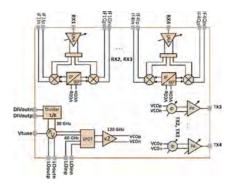

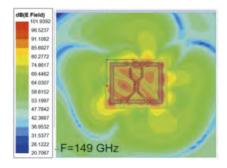

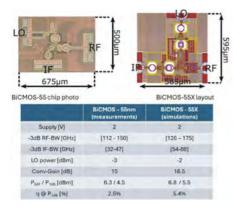

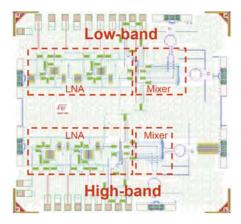

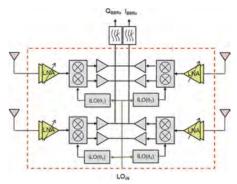

- Giovanni Mangraviti, Cédric Dehos, Vincent Puyal, Olivier Richard, Ghita Yaakoubi khbiza, Francesco Foglia Manzillo, Xuan Viet Linh Nguyen, Francesco Filice, Ettore Noccetti, Pierre-Louis Hellier, Florence Podevin, Sylvain Bourdel, Andrea Ruffino, Kyung-Sik Choi, Basem Abdelaziz Abdelmagid, Mohamed Eleraky, Hua Wang, Bertrand Ardouin, Tom, Keinicke Johansen, Luca Fanori, Qiuting Huang, Erich Schlaffer, Piet Wambacq, Dominique Morche, Björn Debaillie: "Sub-THz transceiver design for future generation mobile communications"

- presents an innovative D-band transceiver circuit and module prototype design based on the most advanced BiCMOS and InP technologies.

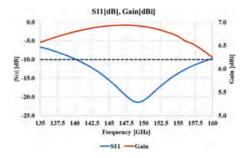

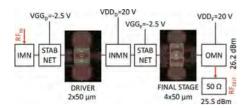

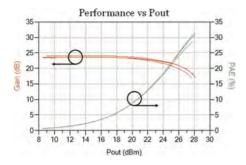

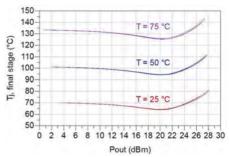

- Francesco Manni, Paolo Colantonio, Rocco Giofrè, Ernesto Limiti, Patrick Ettore Longhi, Steven Mejillones Caicedo, Stefano Moscato, Alessandro Fonte: "Ka-Band GaN-on-SiC Power Amplifier for High EIRP Satellite Phased Antenna Array" presents an innovative a phased antenna array operating in the Ka-band, from 25.5 to 27 GHz enabling the adoption of a custom-designed power amplifier based on 0.15 μm GaN-on-SiC technology capable of delivering ~30% PAE and 28 dBm output power.

<sup>\*</sup> The abstracts are compiled in the appendix of this book.

# **Editors' Biography**

1st Editor: Björn Debaillie, imec, Belgium Björn Debaillie (Senior, IEEE) leads imec's collaborative R&D program on cutting-edge connected computing, covering high speed communications, high resolution sensing, and neuromorphic computing. As a seasoned researcher and manager, he is responsible for strategic collaborations and partnerships, innovation management, and public funding policies as well as the operational management and coordination across

imec's collaborative programs and projects. Björn Debaillie coordinates public funded projects and seeds new initiatives. He holds patents, received awards and authored books and international papers published in various journals and conference proceedings.

**2<sup>nd</sup> Editor:** Philippe Ferrari, Université Grenoble Alpes, France

Philippe Ferrari (Senior, IEEE) received his Ph.D. degree from the "Institut National Polytechnique de Grenoble" (INPG), France, in 1992, with honors. Since 2004, he has been a professor at the University Grenoble Alpes, Grenoble, France. His main research interests concern tunable and miniaturized devices,

such as filters, phase shifters, matching networks, couplers, power dividers and VCOs. These devices are developed in many technologies, PCB, CMOS/BiCMOS, and nanowires, at RF and mm-wave frequencies. He has worked towards the development of slow-wave CPW, and developed new topologies of slow-wave transmission lines, based on microstrip lines and SIWs, respectively. He is author or co-author of more than 300 papers published in international journals or conferences, and co-holder of six patents. He is a member of the Editorial Board of the International Journal on RF and Microwave Computer-Aided Engineering (Wiley), an Associate Editor of the

International Journal of Microwave and Wireless Technologies (EuMA) and member of the Editorial Board of Electronics Letters.

**3rd Editor:** Didier Belot, STMicroelectronics, France Didier Belot first spent 30 years in ST Technology R&D, where he worked initially on characterization-modeling of bipolar transistors before moving to high frequency analog design to develop optical-electronic interfaces. In 1995, he moved to Analog-RF design to work on cellular and Bluetooth transceivers, in SiGe and CMOS respec-

tively. In 2006, he created a joint team with LETI, to initiate the development of mmW R&D prototypes at 60 GHz in CMOS-65, which led to a demonstration of a 4 Gbs wireless link at 60 GHz over 1 m. In 2014, he joined CEA-LETI, to continue his research work, on mmW CMOS, on mmW plastic guides, and, on very high speed mmW (1-10 GBs and more). He has also played an important role in the orientation of the RF and mmW roadmaps. and in the management of programs such as IPCEI within LETI. At the beginning of 2023 he came back to ST in the Technology Design Platform group, in charge of wireless strategy and innovation. Moreover, he has participated and is participating in the elaboration of European and worldwide Roadmaps on Wireless, (NEREID, CORENECT, ECS-SRIA, IRDS, etc). His current research interests include millimeter wave propagation through plastic, sub-THz communications, III-V devices on silicon for mmW and THz applications, and the use of RF for quantum computing. He was a member of the French National Scientific Council "Micro and Nanotechnologies" from 2012 to 2016, a member of various conference program committees such as RFIC, ESSCIRC, ISSCC, IEDM. He is a member of the IEEE-MTT-9 (mmW and THz Devices to System) technology committee and the EuMW technical committee. He is a reviewer for the IEEE MTT and SSC journals, and author or co-author of more than 400 publications and 70 patents.

**4rd Editor:** François Brunier, SOITEC, France François Brunier (Member, IEEE) graduated as a physics and electronics engineer from Centrale-Supelec in 1997. From 1998 to 2002, he worked as device integration engineer for embedded DRAM products in STMicroelectronics Crolles. In 2002, he joined Soitec as head of advanced characterization

laboratory. From 2009 to 2011, as a product manager, he led the RF-SOI and power SOI product development and offering. Since 2012, as a partnership program manager, he is in charge of European collaborative Chips JU programs, IPCEI and public relations.

5<sup>th</sup> Editor: Christophe Gaquiere, MC2-Technologies, France

Christophe Gaquière is currently full professor at the University of Lille and carries out his research activity at the Institut d'Electronique de Microélectronique et de Nanotechnology (IEMN). The topics concern design, fabrication, characterization and modeling of

HEMT's and HBT devices. He works on GaAs, InP, metamorphic HEMT's and now he is involved in the GaN activities. His main activities are microwave characterizations (small and large signal between 1 and 500 GHz) in order to correlate the microwave performances with the technological and topology parameters. Today, his activities concern mainly the investigation of two-dimensional electronic plasmons and gunn like effects for THz solid state GaN based detectors and emitters (HEMT and SSD), AlGaN/GaN nano-wires for microwave applications and MEMS activities based also on GaN. He was responsible for the microwave characterization part of the common laboratory between Thales TRT and IEMN focus on wide band gap semiconductor (GaN, SiC, and Diamond) from 2003 up to 2007. He is in the TPC of several European conferences. He was in charge of the silicon millimeter wave advanced technologies part of the common lab between ST microelectronics and IEMN. He co-founded the company MC2-technolgies in 2004 (95 people) and he is general manager. Christophe Gaquière is the author or co-author of more than 150 publications and 300 communications.

6th Editor: Pierre Busson, STMicroelectronics, France

Pierre Busson (Senior, IEEE) received his M.Sc. degree from the "Ecole Centrale d'Electronique" of Paris France in 1985 and his Ph.D. degree from the University of Rennes, France. In 1993, he worked for CELAR, national military research center, where he was involved in realization of propagation channel

simulator for spread spectrum and frequency hopping. In 1995, he worked for CNET Rennes, national telecommunication research center, for the

#### xxii Editors' Biography

realization of the first integrated demonstrator for terrestrial digital TV with COFDM link. In 1997, he joined STMicroelectronics where he was involved in set-top boxes circuits for terrestrial, satellite and cable. He is currently Wireless RF System/Architect and a Fellow of ST Technical Staff, working on the development of the next generation for wireless system.

**7th Editor:** Urt Steik nien , Teraglobus, Lithuania Urt Steik nien earned her M.S.S. degree from the University of Warwick and began her career as a public sector auditor for PriceWaterhouseCoopers in London. In 2019, she co-founded a start-up focused on developing an FDA-registered medical device for diabetes patients. She holds four patents and is currently a Senior Project Manager at Teraglobus, where

she oversees the execution of large collaborative projects co-funded by the Chips Joint Undertaking and Horizon Europe programmes.

# **List of Contributors**

Abdelaziz Abdelmagid, Basem, ETH Zürich, Switzerland

Aboushady, Hassan, Seamless Waves, France

Adebabay Belie, Ayenew, Université de Montpellier, France

Alcotte, Reynald, imec, Belgium

Ardouin, Bertrand, III-V Lab, France

Baridi, Bachar, CNRS - Université de Lille, France

Bhutani, Akanksha, Karlsruher Institut für Technologie (KIT), Germany

Bilato, Andrea, Università di Pavia, Italy

Blache, Fabrice, III-V Lab, France

Boccardi, Guillaume, imec, Belgium

Boch, Jérôme, Université de Montpellier, France

Bouhouche, Menel, Université de Montpellier, France

Bourdel, Sylvain, Grenoble INP, France; Université Grenoble Alpes, France

Boutry, Hervé, CEA-Leti, France

Braun, Tanja, Fraunhofer IZM, Germany

Brunier, François, Soitec, France

Buchali, Fred, Nokia Network Infrastructure, Germany

Caicedo Mejillones, Steven, SIAE MICROELETTRONICA, Italy

Céli, Didier, STMicroelectronics, France

Centurelli, Francesco, Università di Roma "La Sapienza", Italy

Chauvet, Antoine, III-V Lab, France

Chevalier, Pascal, STMicroelectronics, France

Choi, Kyung-Sik, ETH Zürich, Switzerland

#### xxiv List of Contributors

Colantonio, Paolo, Università di Roma "Tor Vergata", Italy

Collaert, Nadine, imec, Belgium; Vrije Universiteit Brussel, Belgium

Collisi, Michael, Universität des Saarlandes, Germany

Danneville, François, CNRS - Université de Lille, France

Dartizio, Simone Mattia, Politecnico di Milano, Italy

Davy, Nil, III-V Lab, France

De Filippi, Guglielmo, Università di Pavia, Italy

Debaillie, Björn, imec, Belgium

Deglise-Favre, Claire, STMicroelectronics, France

Dehos, Cédric, CEA-Leti, France

Derluyn, Joff, Incize, Belgium

Derrier, Nicolas, STMicroelectronics, France

Ducournau, Guillaume, CNRS - Université de Lille, France

Durand, Cédric, STMicroelectronics, France

Duval, Bernadette, III-V Lab, France

El Beyrouthy, Johnny, Université de Montpellier, France

Eleraky, Mohamed, ETH Zürich, Switzerland

Fanori, Luca, Advanced Circuit Pursuit (ACP), Switzerland

Filice, Francesco, imec, Belgium

Foglia Manzillo, Francesco, CEA-Leti, France

Foissey, Ophélie, STMicroelectronics, France

Fonte, Alessandro, SIAE MICROELETTRONICA, Italy

Gauthier, Alexis, STMicroelectronics, France

Ghyselen, Bruno, Soitec, France

Gianesello, Frederic, STMicroelectronics, France

Giofrè, Rocco, Università di Roma "Tor Vergata", Italy

Gloria, Daniel, STMicroelectronics, France

Goix, Michel, III-V Lab, France

Gomes, Leonardo, Université Grenoble Alpes, France; ST Microelectronics, France

Guitard, Nicolas, STMicroelectronics, France

Haizmann, Andreas, CircularTree, Germany

Hauck, Oliver, Universität des Saarlandes, Germany

Hellier, Pierre-Louis, Université Grenoble Alpes, France

Hersent, Romain, III-V Lab, France

Hobballah, Abdel Hadi, S2P-Smart Plastic Products, France

Huang, Qiuting, Advanced Circuit Pursuit (ACP), Switzerland

Ingels, Mark, imec, Belgium

Johansen, Tom Keinicke, Danmarks Tekniske Universitet, Denmark

Jorge, Filipe, III-V Lab, France

Konczykowska, Agnieszka, III-V Lab, France

Kumar, Annie, imec, Belgium

Kunert, Bernardette, imec, Belgium

Levantino, Salvatore, Politecnico di Milano, Italy

Limiti, Ernesto, Università di Roma "Tor Vergata", Italy

Lodi Rizzini, Daniele , Politecnico di Milano, Italy

Longhi, Patrick, Università di Roma "Tor Vergata", Italy

Mangraviti, Giovanni, imec, Belgium

Manni, Francesco, Università di Roma "Tor Vergata", Italy

Mazzanti, Andrea, Università di Pavia, Italy

Milon, Victor, STMicroelectronics, France

Mismer, Colin, III-V Lab, France

Möller, Michael, Universität des Saarlandes, Germany

Mols, Yves, imec, Belgium

Monsieur, Frederic, STMicroelectronics, France

Monsurrò, Pietro, Università di Roma "La Sapienza", Italy

Morandini, Yvan, Soitec, France

#### xxvi List of Contributors

Morche, Dominique, CEA-Leti, France

Moro, Riccardo, SIAE MICROELETTRONICA, Italy

Moscato, Stefano, SIAE MICROELETTRONICA, Italy

Nguyen, Xuan Viet Linh, CEA-Leti, France

Noccetti, Ettore, imec, Belgium; Università di Pisa, Italy

Nodjiadjim, Virginie, III-V Lab, France

Occello, Olivier, CNRS - Université de Lille, France

Pallotta, Andrea, STMicroelectronics, Italy

Parvais, Bertrand, imec, Belgium; Vrije Universiteit Brussel, Belgium

Pascal, Fabien, Université de Montpellier, France

Peralagu, Uthayasankaran, imec, Belgium

Piotto, Lorenzo, Università di Pavia, Italy

Podevin, Florence, Grenoble INP, France

Puyal, Vincent, CEA-Leti, France

Richard, Olivier, CEA-Leti, France

Riet, Muriel, III-V Lab, France

Roda Neve, César, Soitec, France

Ruffino, Andrea, ETH Zürich, Switzerland

Sadeghi Chameh, Hassan, Università di Roma "La Sapienza", Italy

Sagnes, Bruno, Université de Montpellier, France

Schlaffer, Erich, AT&S, Austria

Sinha, Siddhartha, imec, Belgium

Sonnerat, Florence, STMicroelectronics, France

Suealp, Pelin, AT&S, Austria

Szriftgiser, Pascal, CNRS - Université de Lille, France

Takahashi, Hiroaki, AT&S, Austria

Tesolin, Francesco, Politecnico di Milano, Italy

Tommasino, Pasquale, Università di Roma "La Sapienza", Italy

#### List of Contributors XXVII

Trifiletti, Alessandro, Università di Roma "La Sapienza", Italy

Vais, Abhitosh, imec, Belgium

Valorge, Olivier, CEA-Leti, France

Varonen, Mikko, VTT Technical Research Centre of Finland, Finland

Vermeersch, Bjorn, imec, Belgium

Vivien, Kimon, United Monolithic Semiconductors (UMS), France

Walden, Gunther, CircularTree, Germany

Wambacq, Piet, imec, Belgium; Vrije Universiteit Brussel, Belgium

Wang, Hua, ETH Zürich, Switzerland

Wodaje, Yewulsew Manale, CNRS - Université de Lille, France

Yaakoubi khbiza, Ghita, CEA-Leti, France

Yacoub, Hady, Ferdinand-Braun-Institut, Germany

# **List of Figures**

| Chapter 1 |                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------|

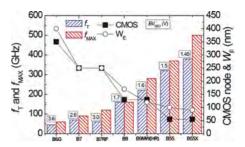

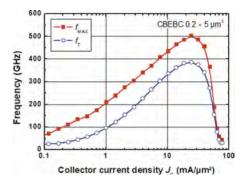

| Figure 1  | STMicroelectronics high-speed SiGe BiCMOS                                                             |

|           | technologies (HBT performance & CMOS node).                                                           |

|           | $W_{\rm E}$ is the physical emitter width. $BV_{\rm CEO}$ is the emitter–                             |

|           | collector breakdown voltage of the HBT with an                                                        |

|           | open base. $f_{\rm T}$ and $f_{\rm MAX}$ correspond to the peak values                                |

|           | measured for the SiGe HBT2                                                                            |

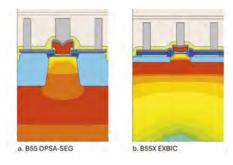

| Figure 2  | TCAD cross-sections of the DPSA-SEG (a) and                                                           |

| J         | EXBIC (b) architectures used in STMicroelectronics                                                    |

|           | B55 and B55X technologies,                                                                            |

|           | respectively                                                                                          |

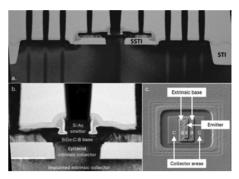

| Figure 3  | B55X SiGe HBT (EXBIC architecture: TEM                                                                |

| J         | cross-sections at the end of fabrication of the whole                                                 |

|           | transistor (a) and zoom-in of the emitter-base                                                        |

|           | area (b) and SEM top view after extrinsic base                                                        |

|           | patterning (c)                                                                                        |

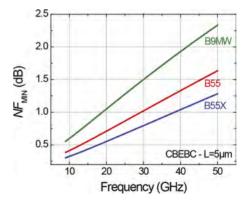

| Figure 4  | Comparison of the evolution of SiGe HBT noise                                                         |

|           | figure with the frequency (CBEBC transistor, $V_{\rm BE}$ =                                           |

|           | 0.82 V) between B9MW, B55, and B55X (data are                                                         |

|           | from the models)                                                                                      |

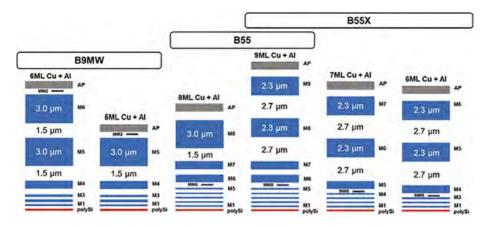

| Figure 5  | Metallization stacks developed in the B9MW, B55,                                                      |

|           | and B55X technologies                                                                                 |

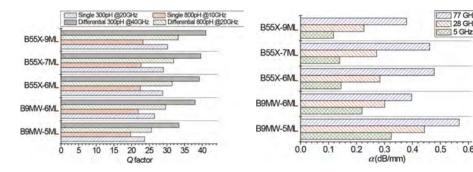

| Figure 6  | Comparison of performance (Q-factor) of single                                                        |

|           | ended and differential inductors of the BEOL stacks                                                   |

|           | of Figure 5                                                                                           |

| Figure 7  | Comparison of performance (attenuation constant $\alpha$ )                                            |

|           | of transmission lines of the BEOL stacks of Figure 5                                                  |

|           | $(Z_c = 50\text{W})$                                                                                  |

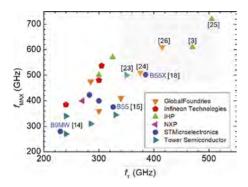

| Figure 8  | $\operatorname{Peak} f_{\operatorname{T}}$ and $f_{\operatorname{MAX}}$ values of high-speed SiGe HBT |

|           | technologies (references are provided for $f_{\rm T}$                                                 |

|           | $> 350 \text{ GHz}$ and $f_{\text{MAX}} > 400 \text{ GHz}$ and ST technologies)7                      |

| Chapter 2 |                                                                                   |

|-----------|-----------------------------------------------------------------------------------|

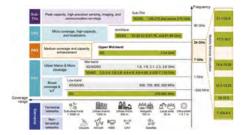

| Figure 1  | Spectrum overview for mobile networks14                                           |

| Figure 2  | Applicability of RF-SOI technology platforms15                                    |

| Figure 3  | Second harmonic as function of the frequency                                      |

|           | comparing HR-SOI with mmWave trap- rich RF-SOI.                                   |

|           | Input power: 15 dBm                                                               |

| Figure 4  | RF substrate figures of merit were measured from                                  |

|           | M1M2 CPW lines. Small-signal data, including α                                    |

|           | (attenuation constant), peff (effective resistivity), and                         |

|           | $\varepsilon_{\text{effsub}}$ (effective relative permittivity of the substrate), |

|           | were extracted using multiline thru-reflect-line                                  |

|           | calibration from multiple CPWs. Large-signal data,                                |

|           | including harmonics H1, H2, and H3, were measured                                 |

|           | at a 900 MHz fundamental frequency on a 2-mm-long                                 |

|           | CPW                                                                               |

| Figure 5  | Piezo on insulator (POI) versus alternative RF filter                             |

|           | technologies benchmarking17                                                       |

| Figure 6  | Electromechanical coupling factors and bulk wave                                  |

|           | velocities for various LiNbO <sub>3</sub> and LiTaO <sub>3</sub> commercial       |

|           | cuts17                                                                            |

| Chapter 3 |                                                                                   |

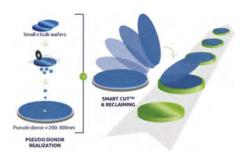

| Figure 1  | Schematic illustration of the Smart Cut technology                                |

| 1 igure 1 | that manufactures SOI substrates22                                                |

| Figure 2  | Smart Cut technology combining an adapted active                                  |

| 115010 2  | layer on a functional support substrate for a less                                |

|           | dependent value chain                                                             |

| Figure 3  | BEYOND5 project consortium partners mapped onto                                   |

| 1 iguie o | the value chain                                                                   |

| Figure 4  | BEYOND5 project demonstrators incorporate the                                     |

| 118010 1  | different RF-SOI and FD-SOI technology flavor23                                   |

| Figure 5  | $4 \times 4$ MIMO TRX 22FDX chip for the in-cabin radar                           |

| 8         | demonstrator developed in the BEYOND5 project23                                   |

| Figure 6  | The block diagram of the designed TRX for the                                     |

| 8         | in-cabin radar demonstrator developed in the                                      |

|           | BEYOND5 project                                                                   |

| Figure 7  | TRX low-noise amplifier noise performance for                                     |

| 8         | the in-cabin radar demonstrator developed in the                                  |

|           | BEYOND5 project                                                                   |

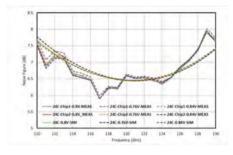

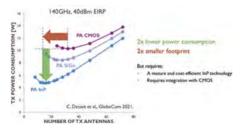

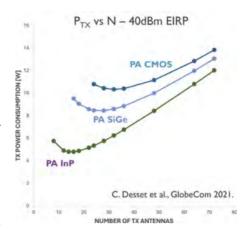

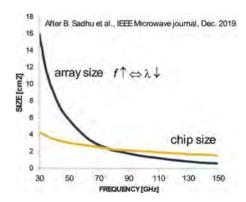

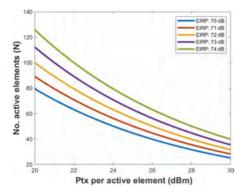

| Figure 8  | Power consumption and footprint PA comparison across different technologies at 140 GHz operation frequency and 40 dBm effective isotropic radiated |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| F: 0      | power                                                                                                                                              |

| Figure 9  | Schematic of the Smart Cut with tiling approach 24                                                                                                 |

| Figure 10 | The Move2THz project consortium illustrated across                                                                                                 |

| D: 11     | the value chain                                                                                                                                    |

| Figure 11 | The Move2THz project aims to break the current                                                                                                     |

|           | vicious cycle, enabling the adoption of InP in large-                                                                                              |

| Figure 12 | volume mass markets                                                                                                                                |

| Figure 12 | The SmartGaN substrate stack-up for optimized                                                                                                      |

|           | power or RF applications                                                                                                                           |

| Chapter 4 |                                                                                                                                                    |

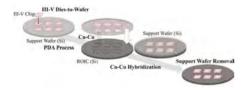

| Figure 1  | An example of heterogenous integration for visible-                                                                                                |

| rigure r  | SWIR image sensor with read-out integrated circuit                                                                                                 |

|           | (ROIC). III-V chip can either be just a diced native                                                                                               |

|           | substrate or a die with already fabricated device.                                                                                                 |

|           | Bonding process can consist of Cu–Cu or oxide–                                                                                                     |

|           | oxide hybrid bonding                                                                                                                               |

| Figure 2  | The $\mu$ -transfer printing process. (a) and (b) The                                                                                              |

| 1194102   | definition of the III-V device on the III-V source                                                                                                 |

|           | wafer. (c) and (d) The structures are encapsulated and                                                                                             |

|           | the release layer is selectively etched. (e) The use of                                                                                            |

|           | a stamp to pick-up arrays of III-V devices from the                                                                                                |

|           | source wafer. (f) Print them onto the silicon photonic                                                                                             |

|           | target wafer, after which the encapsulation is removed                                                                                             |

|           | and the III-V devices are electrically contacted on a                                                                                              |

|           | wafer-scale29                                                                                                                                      |

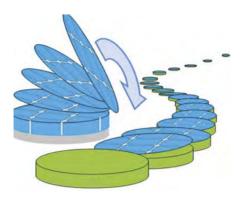

| Figure 3  | Simplified sketch of the production of tiled 200/300                                                                                               |

| Ö         | mm InPOSi wafers                                                                                                                                   |

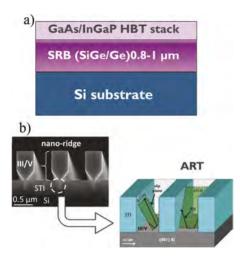

| Figure 4  | (a) An example of SRB-based growth of III-V on                                                                                                     |

| Ö         | Si substrate using a thick buffer layer. (b) Cross-                                                                                                |

|           | sectional SEM image of an NR array. (b) Aspect ratio                                                                                               |

|           | trapping (ART), where defects are trapped in narrow                                                                                                |

|           | trenches                                                                                                                                           |

| Figure 5  | (a) Cross-sectional SEM image of an NR laser array.                                                                                                |

| _         | (b) The impact of sidewall deposition when an HBT                                                                                                  |

|           | device stack is deposited on a free-standing NR.                                                                                                   |

|           | (c) A second oxide pattern on the first prevents                                                       |

|-----------|--------------------------------------------------------------------------------------------------------|

|           | sidewall growth. (d) HAADF-STEM (high-angle                                                            |

|           | annular dark-field scanning transmission electron                                                      |

|           | microscopy) image of a GaAs-based NR HBT                                                               |

| Figure 6  | (a) HAADF-STEM of GaAs/InGaP HBT stack                                                                 |

| J         | after epitaxial deposition on 300 mm (100) silicon                                                     |

|           | substrate along and across a nano-ridge. (b) A                                                         |

|           | comparison of electrical characterization (Gummel                                                      |

|           | plot) of the devices fabricated in this work with that                                                 |

|           | of ref (c) A comparison of DC current gain, β, of                                                      |

|           | our HBT with that of ref. [6] with respect to collector                                                |

|           | current                                                                                                |

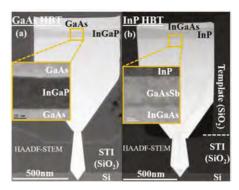

| Figure 7  | HAADF-STEM pictures of (a) GaAs and (b) InP                                                            |

| S         | HBT stacks on 300 mm Si substrate across a single                                                      |

|           | nano-ridge (NR) showing good device layers                                                             |

|           | interface quality33                                                                                    |

| Figure 8  | (a) Gummel plots of HBTs fabricated on GaAs and                                                        |

| J         | InP NRE material stack. The output characteristic                                                      |

|           | of GaAs HBT is also shown in the inset. (b) Across                                                     |

|           | wafer variation of DC current gain and maximum                                                         |

|           | collector current of a GaAs NRE HBT wafer. (c)                                                         |

|           | Key DC parameters variation of GaAs (left) and InP                                                     |

|           | (right) NRE HBTs                                                                                       |

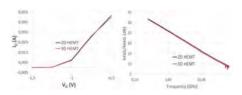

| Figure 9  | (a) Transfer and (b) output characteristics of an                                                      |

|           | NR-HBT fabricated on In <sub>0.78</sub> Ga <sub>0.22</sub> P/GaAs <sub>0.72</sub> Sb <sub>0.28</sub> / |

|           | In <sub>0.30</sub> Ga <sub>0.70</sub> As stack. (c) A comparison of the Gummel                         |

|           | plots of HBTs fabricated on three different III-V                                                      |

|           | material systems to illustrate the improvement of                                                      |

|           | on current in In <sub>0.3</sub> Ga <sub>0.7</sub> As NR HBTs as compared to                            |

|           | GaAs NR HBTs34                                                                                         |

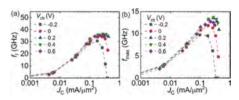

| Figure 10 | (a) $f_{\rm t}$ and (b) $f_{\rm max}$ for a device with $W_{\rm E}$ :                                  |

|           | 5 $\mu$ m and 55 nano-ridges ( $L_{\rm E}$ : 44 $\mu$ m) as functions of                               |

|           | current density $J_{\rm C}$ . At $V_{\rm cb} = \bar{0}.4$ V, extracted peak $f_{\rm t}$ is             |

|           | $\sim$ 36 GHz and peak $f_{\text{max}}$ is 13.7 GHz34                                                  |

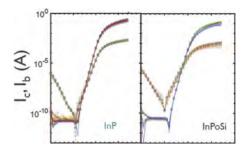

| Figure 11 | Transfer characteristics of a InP/GaAsSb/InP HBT                                                       |

|           | fabricated on InP (left) and InPoSi (right) substrates.                                                |

|           | Except for the difference in base current ideality                                                     |

|           | factor and leakage, ON state performances of both are                                                  |

|           | quite similar and good35                                                                               |

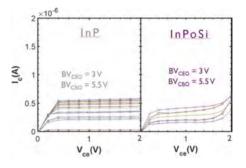

| Figure 12            | Output characteristics of an InP/GaAsSb/InP HBT fabricated on InP (left) and InPoSi (right) substrates for the same base currents. Note the slight difference in the output current |

|----------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Chapter 5            |                                                                                                                                                                                     |

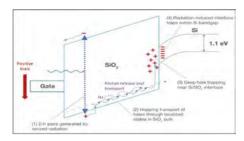

| Figure 1             | Process of radiation-induced charge generation in MOS devices                                                                                                                       |

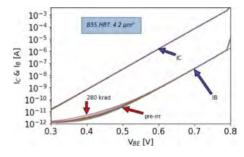

| Figure 2             | Pre- and post-irradiation forward Gummel plot of $0.42 \times 10 \ \mu\text{m}^2 \ B55 \ HBT$                                                                                       |

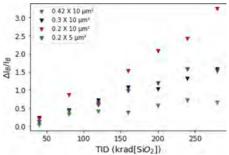

| Figure 3             | Examples of: (a) $\Delta I_{\text{C}}I_{\text{C}}$ and (b) $\Delta I_{\text{B}}I_{\text{B}}$ versus $V_{\text{BE}}$ at different TIDs                                               |

| Figure 4<br>Figure 5 | $\Delta I_B I_B$ versus TID at $V_{BE}$ =0.54 V for HS devices                                                                                                                      |

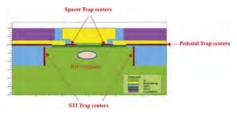

| Figure 6             | HBT                                                                                                                                                                                 |

| Figure 7             | HBTs                                                                                                                                                                                |

| Figure 8             | = 0.4, 0.54, and 0.62 V                                                                                                                                                             |

| Figure 9             | $(A_E = 2 \mu m^2 \text{ at } I_B \text{ of } 100 \text{ nA})$                                                                                                                      |

| Figure 10            | after X-ray exposure                                                                                                                                                                |

| Figure 11            | $(A_E - 3 \mu m)$                                                                                                                                                                   |

| Figure 12            | technology (B9MW) is given                                                                                                                                                          |

| Chapter 6            |                                                                                                                                                                                     |

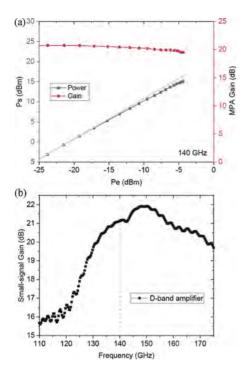

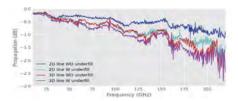

| Figure 1             | (a) Small-signal gain of the DUT, in the whole WR6.5 (110–170 GHz) band. (b) DUT power curve at                                                                                     |

|                      | 140 GHz54                                                                                                                                                                           |

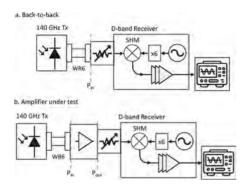

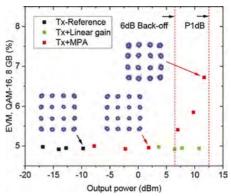

| Figure 2 Figure 3 | (a) Back-to-back measurement in MSA analysis.  (b) Evaluation of the EVM obtained using the amplifier under-test. SHM: Sub-harmonic mixer is used to down-convert the signal from 140 GHz to an intermediate frequency, further detected on a w wideband real-time oscilloscope. The attenuator is used to optimize the power injected into the receiver |

|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                   | lines show the $P_{1dB}$ and 6 dB back-off from $P_{1dB}$ 55                                                                                                                                                                                                                                                                                             |

| Chapter 7         |                                                                                                                                                                                                                                                                                                                                                          |

| Figure 1          | Overview of scopes and emissions across a                                                                                                                                                                                                                                                                                                                |

|                   | value chain60                                                                                                                                                                                                                                                                                                                                            |

| Figure 2          | Net-zero/carbon neutrality target dates of selected                                                                                                                                                                                                                                                                                                      |

|                   | chip manufacturers60                                                                                                                                                                                                                                                                                                                                     |

| Figure 3          | Exemplary upstream supply chain62                                                                                                                                                                                                                                                                                                                        |

| Figure 4          | CARE decarbonization cycle                                                                                                                                                                                                                                                                                                                               |

| Chapter 8         |                                                                                                                                                                                                                                                                                                                                                          |

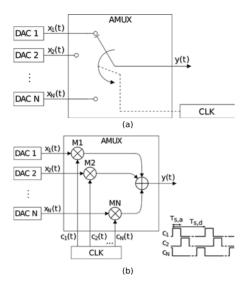

| Figure 1          | (a) N:1 AMUX principle as a clocked toggle switch.                                                                                                                                                                                                                                                                                                       |

| 8                 | (b) Illustration of the <i>N</i> :1 AMUX as mixers with                                                                                                                                                                                                                                                                                                  |

|                   | added output. In case of the 2:1 AMUX, only two, for                                                                                                                                                                                                                                                                                                     |

|                   | the 4:1 AMUX, four mixers are present 69                                                                                                                                                                                                                                                                                                                 |

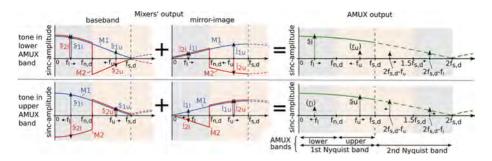

| Figure 2          | Spectra at the AMUX-output of a 2:1 AMUX70                                                                                                                                                                                                                                                                                                               |

| Figure 3          | Example of an amplitude mismatch                                                                                                                                                                                                                                                                                                                         |

| Figure 4          | Basic types of ENoB vs. frequency characteristics of                                                                                                                                                                                                                                                                                                     |

|                   | a 2:1 AMUX. (a) Diverged, d-type, and joined, j-type.                                                                                                                                                                                                                                                                                                    |

|                   | (b) Tilted and translated, t-, and bathtub, b-type                                                                                                                                                                                                                                                                                                       |

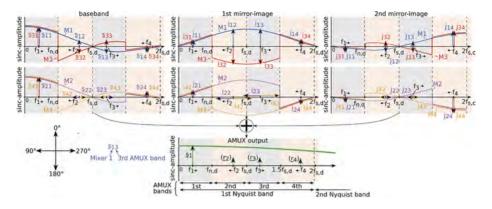

| Figure 5          | Composition of the AMUX-output spectrum of a 4:1                                                                                                                                                                                                                                                                                                         |

|                   | AMUX for a tone $f_1$ in the first AMUX band. The                                                                                                                                                                                                                                                                                                        |

|                   | frequencies $f_2$ , $f_3$ , and $f_4$ are the alias tones in the other                                                                                                                                                                                                                                                                                   |

|                   | AMUX bands. The $\underline{i}$ and $\underline{j}$ represent first and second                                                                                                                                                                                                                                                                           |

|                   | mirror-image tones, respectively. Dotted lines for                                                                                                                                                                                                                                                                                                       |

|                   | M2,4 represent the sinc-envelopes phase-shifted by                                                                                                                                                                                                                                                                                                       |

|                   | 90°/270° in the up/downward direction72                                                                                                                                                                                                                                                                                                                  |

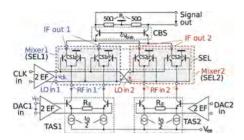

| Figure 6  | Circuit principle of the 2:1 AMUX core realized by                   |

|-----------|----------------------------------------------------------------------|

| J         | the clocked-SEL concept                                              |

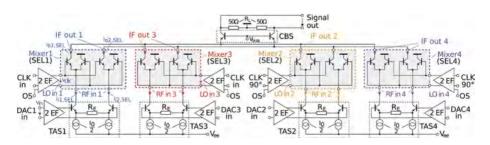

| Figure 7  | Circuit principle of the proposed 4:1 AMUX core                      |

|           | realized by the clocked-SEL concept                                  |

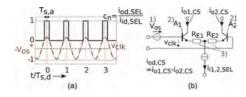

| Figure 8  | (a) Clock voltage with offset and resulting idealized                |

|           | sampling signal $c_n(t)$ for a 4:1 AMUX. (b) Three                   |

|           | methods to introduce an offset to the transfer                       |

|           | characteristic of a CS by (1) offset voltage $V_{os}$ ,              |

|           | (2) different transistor areas $A_1$ , $A_2$ , or (3) different      |

|           | emitter degeneration resistors $R_{E1}$ , $R_{E2}$                   |

| Figure 9  | Chip layout (a), AMUX IC bondwire assembly (b),                      |

|           | and RF-module (c)                                                    |

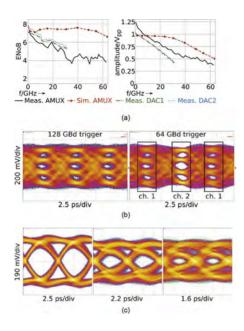

| Figure 10 | (a) ENoB and amplitude curves at 128 GS/s. (b) PAM-4                 |

|           | 128 GS/s eye diagrams, triggered to 128 GBaud (left)                 |

|           | and triggered to 64 GBaud (right). (c) PAM-2 eye                     |

|           | diagrams for 120/140/186 GS/s, respectively                          |

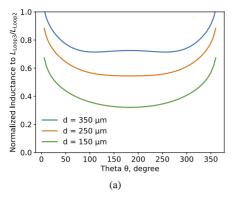

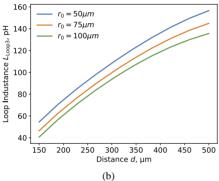

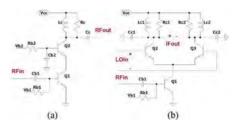

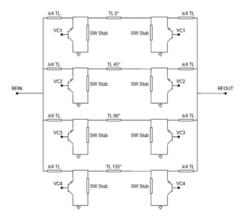

| Chapter 9 |                                                                      |